- Полусумматор

-

Полусумматор — логическая схема, имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Полусумматор используется для построения двоичных сумматоров. Полусумматор позволяет вычислять сумму A+B, где A и B — это разряды двоичного числа, при этом результатом будут два бита S и C, где S — это бит суммы по модулю 2, а C — бит переноса. Однако, как можно заметить, для построения схемы двоичного сумматора (трёхразрядный сумматор, тринарный сумматор) необходимо иметь элемент, который суммирует три бита A, B и C, где C — бит переноса из предыдущего разряда, таким элементом является полный двоичный сумматор, трёхступенчатая разновидность которого состоит из двух полусумматоров и логического элемента 2ИЛИ.

Содержание

История

- 1939 год — Джордж Штибиц (Georg Stibits) из компании Bell Laboratories создал первый двоичный полусумматор "Model K Аdder" на двух электромеханических реле [1].

- 1958 год — в МГУ (мехмат) Н. П. Брусенцов построил первую электронную троичную ЭВМ «Сетунь» с первым электронным троичным полусумматором[2].

Двоичный полусумматор

Двоичный полусумматор может быть определён тремя способами:

1. табличным, в виде таблицы истинности,

2. аналитическим, в виде формулы (СДНФ),

3. графическим, в виде логической схемы.

Так как формулы и схемы могут преобразовываться, то, одной таблице истинности двоичного полусумматора могут соответствовать множества различных формул и схем. Поэтому, табличный способ определения двоичного полусумматора является основным.Двоичный полусумматор представляет собой объединение двух бинарных (двухоперандных) двоичных логических функций: сумма по модулю два - S и разряд переноса при двоичном сложении - C.

x0=A 1 0 1 0 x1=B 1 1 0 0 Название действия (функции) Номер функции S 0 1 1 0 Бит суммы по модулю 2 F2,6 C 1 0 0 0 Бит переноса F2,8 Ненулевой перенос образуется в 1-м случае из 4-х.

СДНФ суммы по модулю 2:

СДНФ бита переноса:

Полусумматор Штибица "Model K Аdder"

Полусумматор Штибица "Model K Аdder" состоит: из двух последовательно соединённых гальванических элементов, по 1,5 Вольта каждый, с суммарным напряжением 3 Вольта, двух кнопок для ввода двух битов аргументов A и B, двух электромагнитных реле, выполняющих бинарную двоичную логическую функцию сложения по модулю 2 и бинарную двоичную логическую функцию бита переноса при двоичном сложении, и двух лампочек накаливания с напряжением 3 Вольта для индикации бита суммы по модулю 2 (S) и бита переноса (C)[1].

Троичный полусумматор

Так как существуют две троичных системы счисления - несимметричная, в которой в разряде переноса не бывает значения больше "1" и симметричная (Фибоначчи), в которой в разряде переноса возможны все три состояния трита, и, как минимум, три физических реализации троичных систем - трёхуровневая однопроводная, двухуровневая двухпроводная (BCT) и двухуровневая трёхбитная одноединичная, то и троичных полусумматоров может быть большое множество.

Троичный полусумматор в несимметричной троичной системе счисления представляет собой объединение двух бинарных троичных логических функций - «сложение по модулю 3» и «разряд переноса при троичном сложении».

x1=x 2 2 2 1 1 1 0 0 0 x0=y 2 1 0 2 1 0 2 1 0 Название действия (функции) Номер функции S 1 0 2 0 2 1 2 1 0 Трит суммы по модулю 3 C 1 1 0 1 0 0 0 0 0 Трит переноса Троичный полусумматор в симметричной троичной системе счисления представляет собой объединение двух бинарных троичных логических функций - «младший разряд (трит) суммы (разности)» и «старший разряд (трит) суммы (разности) (разряд переноса при сложении в троичной симметричной системе счисления)».

x1=x 1 1 1 0 0 0 7 7 7 x0=y 1 0 7 1 0 7 1 0 7 Название действия (функции) Номер функции S 7 1 0 1 0 7 0 7 1 Младший трит суммы F710107071=F-4160 C 1 0 0 0 0 0 0 0 7 Старший трит суммы (трит переноса) F100000007=F6560 "7" обозначает "-1"

Ненулевой перенос образуется в 2-х случаях из 9-ти.

Троичный трёхуровневый полусумматор описан в [3].Троичный двухбитный двухпроводный бинарный (двухоперандный) одноразрядный (BCT) полусумматор, работающий в несимметричной троичной системе счисления приведён в [4], в разделе BCT Addition, в подразделе (f) Circuit diagram и, с ошибочным названием "двухразрядный BCT сумматор", в [5] на рис.3.

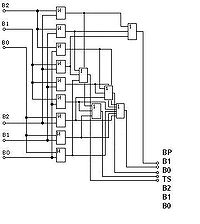

На рисунке справа приведена схема троичного несимметричного полусумматора в трёхбитной одноединичной системе троичных логических элементов, описанного в [6][7].

Троичный зеркально-симметричный одноразрядный полусумматор описан в [8].

См. также

Ссылки

- ↑ 1 2 http://www.computerhistory.org/collections/accession/XD127.80 Computer History Museum

- ↑ http://www.computer-museum.ru/histussr/setun2.htm Малая автоматическая цифровая машина “Сетунь”. Н. П. Брусенцов, Е. А. Жоголев, В. В. Веригин, С. П. Маслов, А. М. Тишулина

- ↑ http://spanderashvili.narod.ru/PA.pdf Астраханский Государственный Технический Университет, Кафедра "Автоматизированные системы обработки информации и управления", Курсовая работа по дисциплине "Объектно-ориентированное проограммирование" по специальности 220200 "Автоматизированные системы обработки информации и управления", Выполнили Морозов А.В., Спандерашвили Д.В., Алтуфьев М.Ю., Проверил к.т.н., доц. Лаптев В.В., Гл.XXIV Троичный полусумматор. Астрахань-2001 г.

- ↑ http://www.dcs.gla.ac.uk/~simon/teaching/CS1Q-students/systems/tutorials/tut3sol.pdf CS1Q Computer Systems

- ↑ http://314159.ru/kushnerov/kushnerov1.pdf Троичная цифровая техника. Ретроспектива и современность

- ↑ Троичный бинарный сумматор в троичной несимметричной системе счисления в трёхбитной системе троичных логических элементов. А.Куликов

- ↑ http://andserkul.narod2.ru/troichnie_summatori/ А.С.Куликов. Троичные сумматоры

- ↑ Компьютеры Фибоначчи. Троичное зеркально-симметричное сложение и вычитание

Категории:- Компьютерная арифметика

- Цифровые интегральные схемы

Wikimedia Foundation. 2010.